时序决定数据的读写速度,两条容量和频率一样的内存,时序越低,性能就越好。

看主办。cpu

简单举例来说。频率,是你一秒搬东西能搬几趟。时序,是你搬东西每到一点需要停下来办个手续,时序越小,停下来的时间越短,速度越快。

频率和时序可以说是内存条两个最重要的参数了

对于频率,很多爱好者多少了解一些。

但了解时序的人就要少许多。

如果只是为了选购,而不想深入了解,可以简单概括:

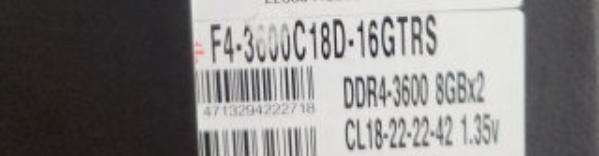

时序由3到5个数字表示(如下图所示,一般是4个数字)。

这几个数字都代表延迟,单位是时钟周期(注意:时钟周期不是时间单位,如果要比较的话,需要把时钟周期换算成时间单位。比如对于DDR3 3000的内存条,1时钟周期=0.666……ns,而对于DDR3 2666的内存条,1时钟周期=0.75ns。)。

既然是延迟,当然越小越好。

在频率相同的情况下,这几个数字越小,内存越快。

(频率不同的话,需要按上面的方法换算)

接下来是详细介绍:

时序的5个数字从左到右分别代表:

(未完,待续……)

内存条时序简单来说只要看第一个CL18这个就好了,这个数字当然是越小越,CL表示就是延迟的长短,很多小伙伴都说时序越低,比如在同频率的CL值越小内存条的性能越好! 不过cl值越大所以频率也会越高!

简单来说没钱就看频率,有钱就看时序!毕竟时序越低的内存条价格也是越贵!

比如皇家戟的内存条时序就是CL18的,很多小伙伴都比较喜欢这个颜值,时序啥的都不在乎!

不过预算低的小伙伴都是不看时序只看频率,比如海盗船的还是不错的!支持xmp的超频!现在基本上ddr4能选择的也就这些,以后ddr5未来可期!

Copyright © 2002-2022 博猫-博猫娱乐纸糊模型站 版权所有 非商用版本备案号:点ICP备7845159号网站地图

扫一扫咨询微信客服

扫一扫咨询微信客服